Product Summary

The 74LVC16241ADL+112 is a high-performance, low power, low voltage, Si-gate CMOS device, superior to most advanced CMOS compatible TTL families. Inputs can be driven from either 3.3 or 5 V devices. In 3-state operation, outputs can handle 5 V. These features allow the use of these devices as a mixed 3.3 and 5 V environment. The 74LVC16241ADL+112 is a 16-bit non-inverting buffer/line driver with 3-state outputs. The device can be used as four 4-bit buffers, two 8-bit buffers or one 16-bit buffer. The 3-state outputs of the 74LVC16241ADL+112 are controlled by the output enable inputs 1OE, 2OE, 3OE and 4OE. A HIGH on nOE causes the outputs to assume a high-impedance OFF-state.

Parametrics

74LVC16241ADL+112 absolute maximum ratings: (1)VCC supply voltage: -0.5 min. +6.5 V max.; (2)IIK input diode current: When VI < 0, -50 mA max.; (3)VI input voltage: note 1 -0.5 min. +6.5 V max.; (4)IOK output diode current VO > VCC or VO < 0, ±50 mA max.; (5)VO output voltage output: HIGH or LOW state; note 1 -0.5 VCC + 0.5 V; (6)output 3-state; note 1 -0.5 +6.5 V; (7)IO output source or sink current: VO = 0 to VCC - ±50 mA; (8)ICC, IGND VCC or GND current: - ±100 mA; (9)Tstg storage temperature: -65 +150℃; (10)Ptot power dissipation: Tamb = -40 to +125℃; note 2 - 500 mW.

Features

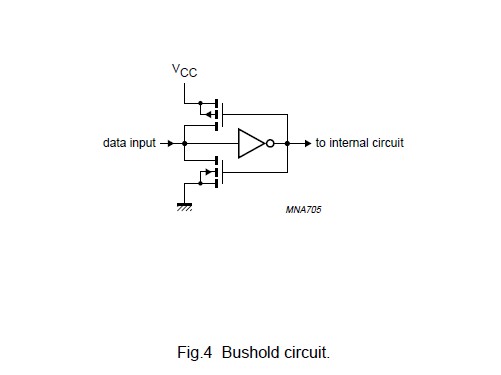

74LVC16241ADL+112 features: (1)5 V tolerant inputs/outputs for interfacing with 5 V logic; (2)Wide supply voltage range from 1.2 to 3.6 V; (3)CMOS low power consumption; (4)MULTIBYTE flow-through standard pin-out architecture; (5)Low inductance multiple power and ground pins for minimum noise and ground bounce; (6)Direct interface with TTL levels; (7)Inputs accept voltages up to 5.5 V; (8)Integrated 30 W termination resistors; (9)All data inputs have bushold (74LVCH162244A only); (10)Complies with JEDEC standard no. 8-1A; (11)ESD protection: HBM EIA/JESD22-A114-A exceeds 2000 V; MM EIA/JESD22-A115-A exceeds 200 V; (12)Specified from -40 to +85℃ and -40 to +125 ℃.

Diagrams

|

74LV00 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74LV00BQ,115 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) 3.3V QUAD 2-INPUT |

Data Sheet |

|

|

||||||||||||

|

74LV00D |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74LV00D,112 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2-INPUT NAND |

Data Sheet |

|

|

||||||||||||

|

74LV00D,118 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2-INPUT NAND |

Data Sheet |

|

|

||||||||||||

|

74LV00DB,112 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2-INPUT NAND |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))