Product Summary

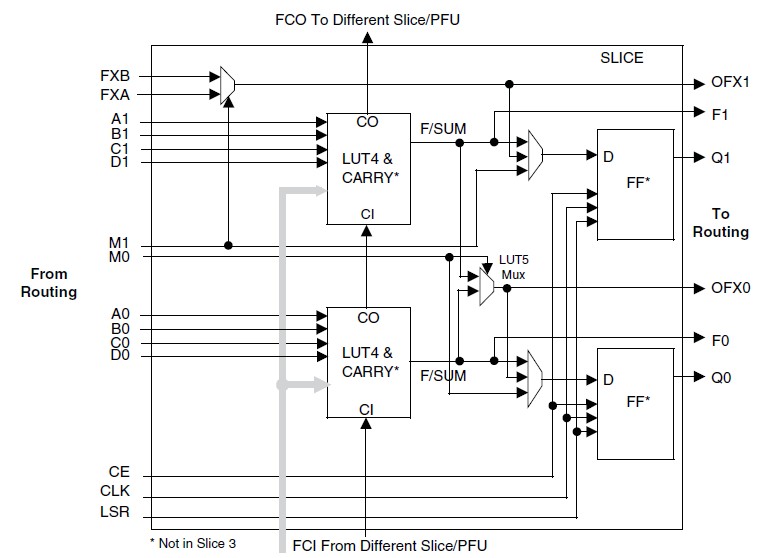

The LFE2M35E-5FN484C is a Field-Programmable Gate Array. It is optimized to deliver high performance features such as advanced DSP blocks, high speed SERDES and high speed source synchronous interfaces in an economical FPGA fabric. The LFE2M35E-5FN484C fabric is optimized with high performance and low cost in mind. The LFE2M35E-5FN484C includes LUT-based logic, distributed and embedded memory, Phase Locked Loops (PLLs), Delay Locked Loops (DLLs), pre-engineered source synchronous I/O support, enhanced sysDSP blocks and advanced configuration support, including encryption and dual boot capabilities.

Parametrics

LFE2M35E-5FN484C absolute maximum ratings: (1)Supply Voltage VCC: -0.5 to 1.32V; (2)Supply Voltage VCCAUX: -0.5 to 3.75V; (3)Supply Voltage VCCJ: -0.5 to 3.75V; (4)Output Supply Voltage VCCIO: -0.5 to 3.75V; (5)Input or I/O Tristate Voltage Applied: -0.5 to 3.75V; (6)Storage Temperature (Ambient): -65 to 150℃; (7)Junction Temperature (Tj): +125℃.

Features

LFE2M35E-5FN484C features: (1)High Logic Density for System Integration; (2)Embedded SERDES (LatticeECP2M Only); (3)sysDSP Block; (4)Flexible Memory Resources; (5)sysCLOCK Analog PLLs and DLLs; (6)Pre-Engineered Source Synchronous I/O; (7)Programmable sysI/O Buffer Supports Wide Range Of Interfaces; (8)Flexible Device Configuration; (9)Optional Bitstream Encryption; (10)System Level Support.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

LFE2M35E-5FN484C |

Lattice |

FPGA - Field Programmable Gate Array 34K LUTs SERDES MEM DSP 1.2V -5 Spd |

Data Sheet |

|

|

||||||||||

|

LFE2M35E-5FN484CES |

Lattice |

FPGA - Field Programmable Gate Array 34K LUTs SERD Mem DS P 1.2V -5 Spd ES |

Data Sheet |

Negotiable |

|

||||||||||

(China (Mainland))

(China (Mainland))