Product Summary

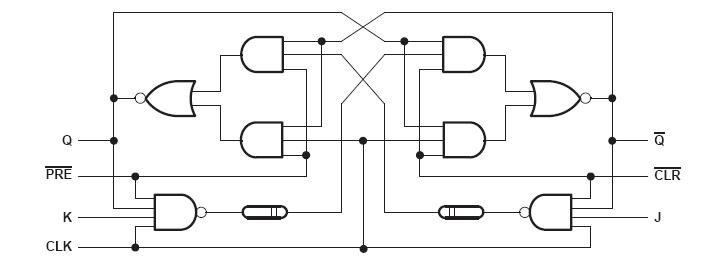

The SN74F112DR is a dual Negative-Edge-Triggered J-K flip-flop with clear and preset. The SN74F112DR contains two independent J-K negative-edge-triggered flip-flops. A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the J and K inputs meeting the setup time requirements is transferred to the outputs on the negative-going edge of the clock pulse. Clock triggering occurs at a voltage level and is not directly related to the rise time of the clock pulse. Following the hold-time interval, data at the J and K inputs may be changed without affecting the levels at the outputs. The SN74F112 can perform as a toggle flip-flop by tying J and K high. The SN74F112DR is characterized for operation from 0℃ to 70℃.

Parametrics

SN74F112DR absolute maximum ratings: (1)Supply voltage range, VCC:-0.5V to 7V; (2)Input voltage range, VI: -1.2V to 7V; (3)Input current range: -30mA to 5mA; (4)Voltage range applied to any output in the high state:-0.5V to VCC; (5)Current into any output in the low state: 40mA; (6)Operating free-air temperature range: 0℃ to 70℃; (7)Storage temperature range:-65℃ to 150℃.

Features

SN74F112DR features: Package Options Include Plastic Small-Outline Packages and Standard Plastic 300-mil DIPs.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

SN74F112DR |

Texas Instruments |

Flip Flops Dual Neg-Edge-Trig J-K Flip-Flop |

Data Sheet |

|

|

||||||||||||

|

SN74F112DRE4 |

Texas Instruments |

Flip Flops Dual Neg-Edge-Trig J-K Flip-Flop |

Data Sheet |

|

|

||||||||||||

|

SN74F112DRG4 |

Texas Instruments |

Flip Flops Dual J K NEG Edge Triggered FlipFlop |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))